リジッドフレキ基板の2次元・3次元 SI/PI評価

リジッドフレキ基板はリジッド基板とFPC(Flexible Printed Circuit:フレキ基板)が一体化した基板です。 部品実装性に優れるリジッド部と屈曲性に優れるフレキシブル基板の部分に分かれているため、小型デバイス内の高密度実装に広く用いられています。

本トピックスでは小型IoTデバイス内のリジッドフレキ基板を想定し、CST Studio Suiteによって2次元及び3次元のSI/PI解析を行うソリューションのご紹介を致します。

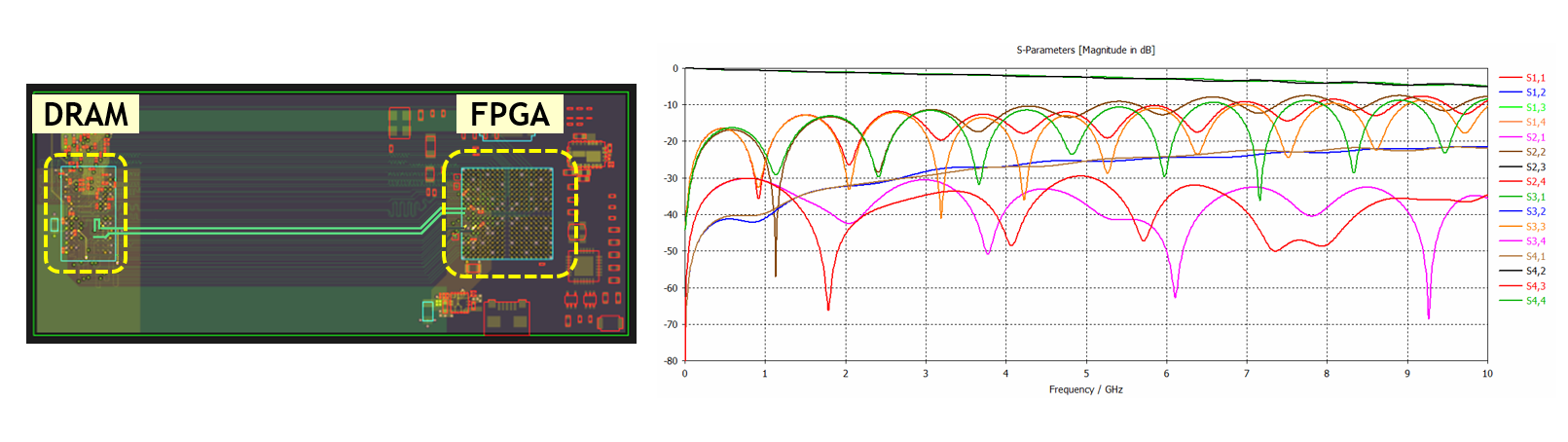

解析対象のリジッドフレキ基板モデル

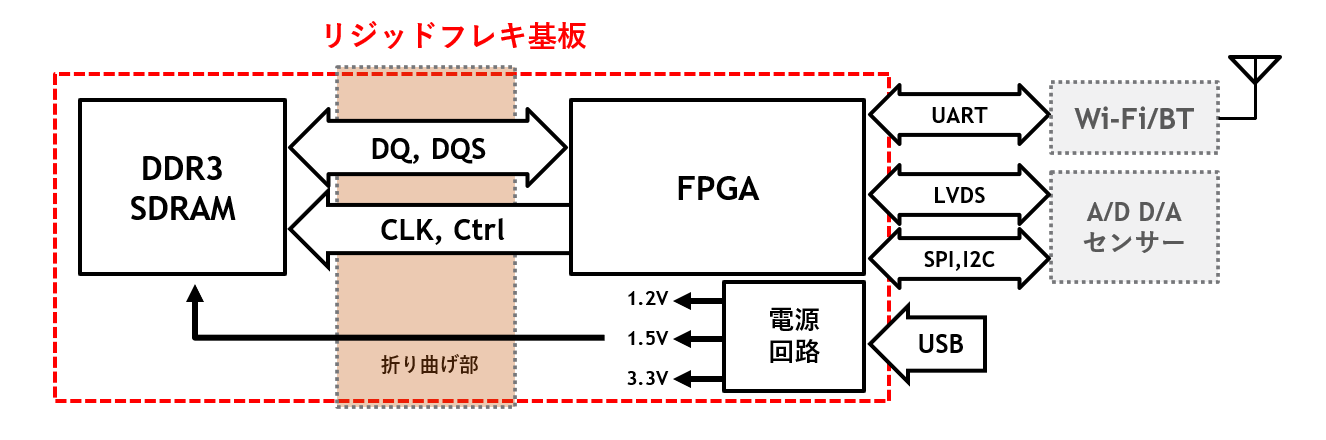

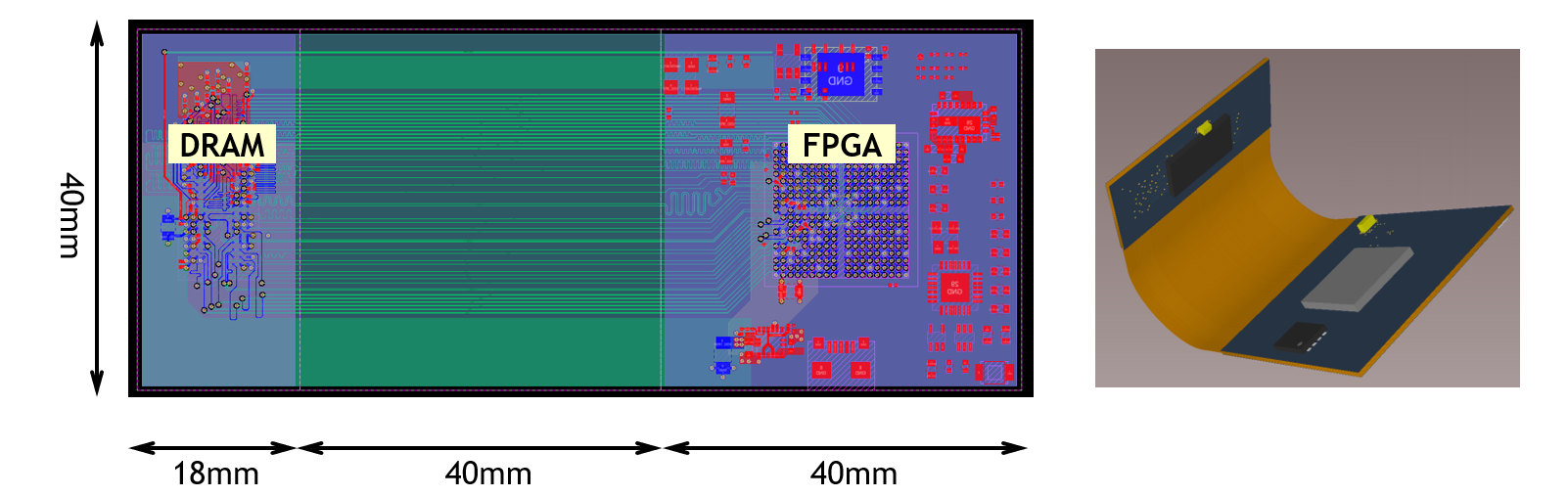

Wi-Fi及びBluetoothによる無線通信とセンサーによるアナログ信号処理を行うFPGAとメモリモジュールがFPC部を介して接続されているリジッドフレキ基板を想定しました。 基板はAltium Designerで設計しました。

2次元のSI/PI解析

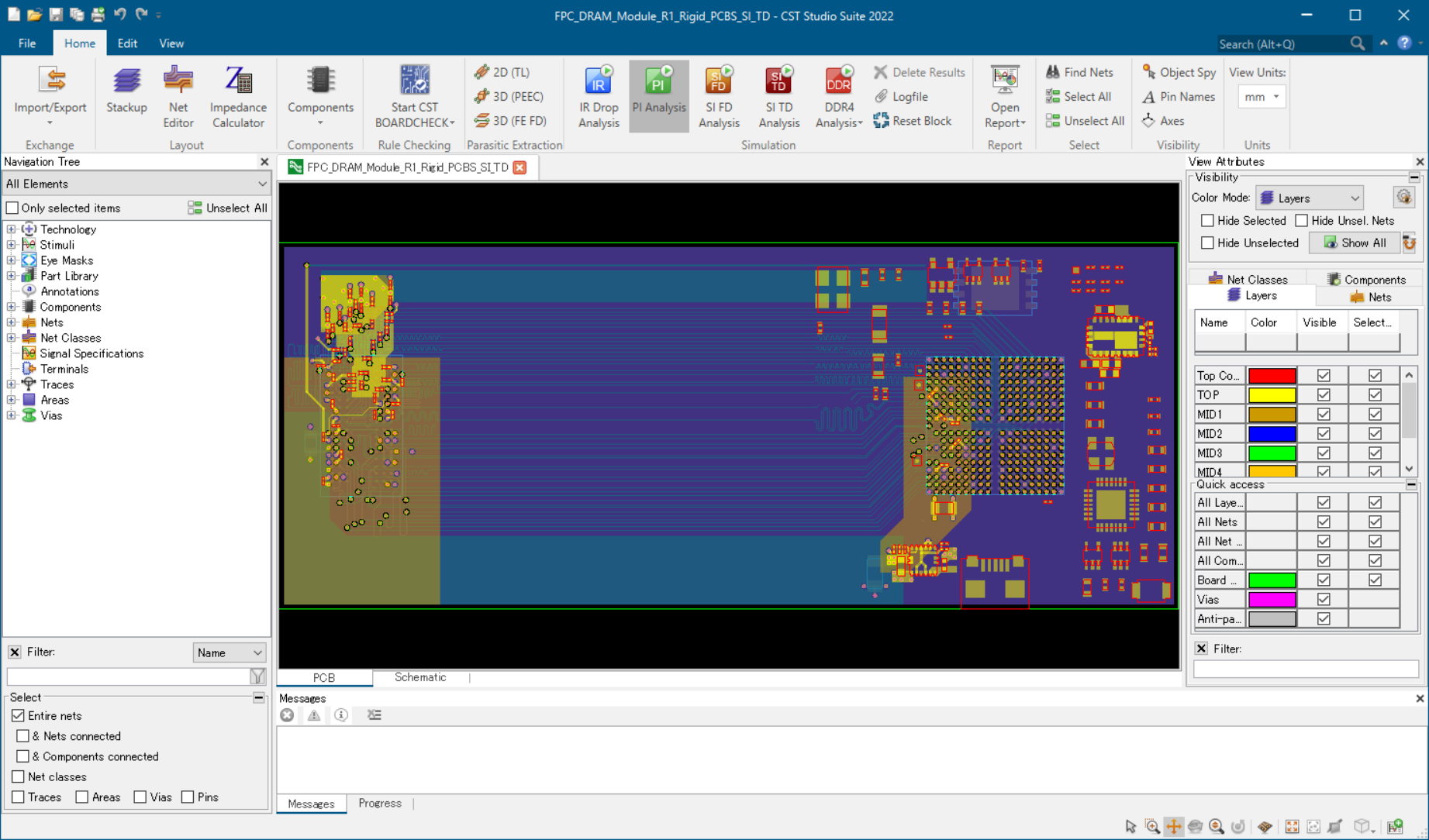

基板のSI/PI解析を行うCST Studio Suiteのモジュール PCB StudioにODB++形式のデータを用いてインポートします。 材質を含むレイヤ情報、ネット情報や実装部品についても自動的に読み込まれます。

IR Drop解析によるPDN評価

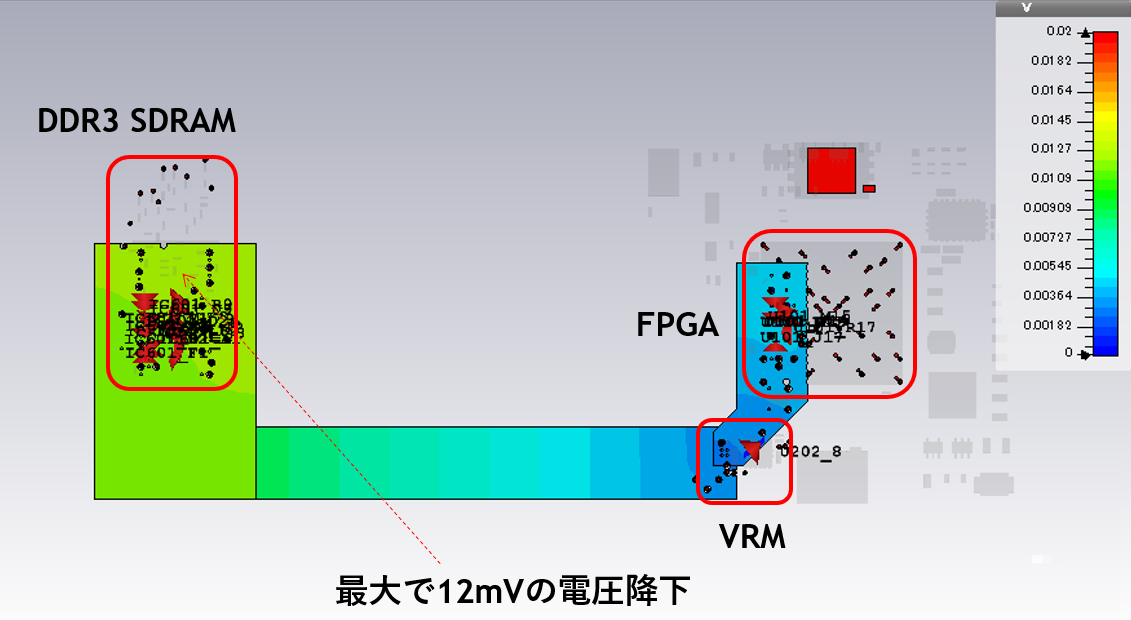

PDN(Power Delivery Network:電源供給回路網)のDC特性としてIR Drop(電源配線抵抗及びデバイスの電力消費に伴う電圧低下)を解析します。 FPGA及びDRAMチップのI/Oピンにおける消費電流を設定してVRMからみた電圧降下をプロットした結果が以下の図です。 DRAM側で最大12mVの電圧降下を確認しました。

電源インピーダンス解析

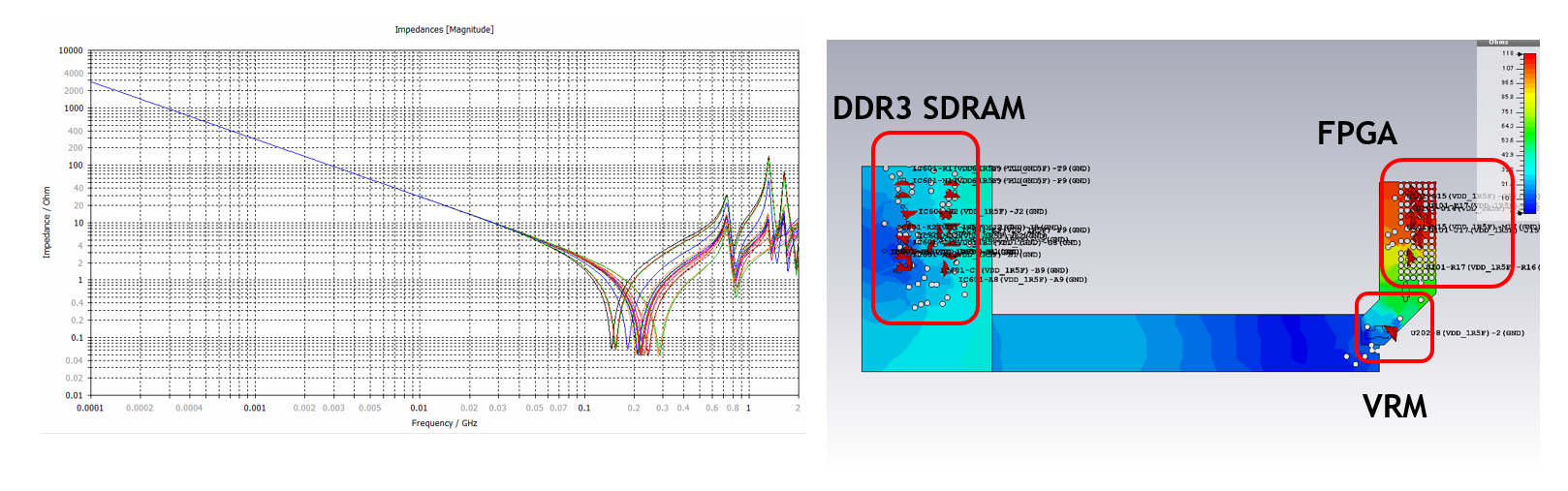

次にPDNのAC特性として電源インピーダンスの周波数特性を解析します。 まずは実装されているキャパシタを全て外した場合の基板単体としての電源インピーダンスを求めます。 インピーダンスが高くなっている1.32GHzでのインピーダンスマップを観察してみます。 FPGA側で高くなっていることが確認出来ました。

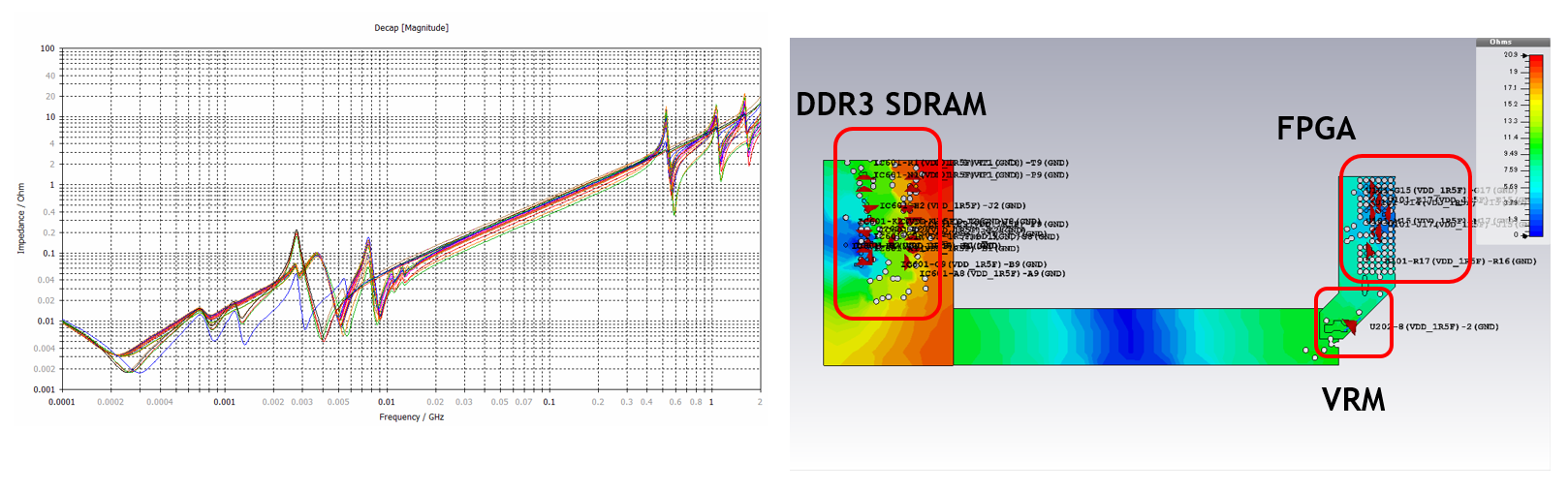

次にキャパシタを実装した状態の電源インピーダンス結果を示します。 同様にインピーダンスが高くなっている1.59GHzでのインピーダンスマップを観察するとDRAM側で高くなっていることが確認出来ました。

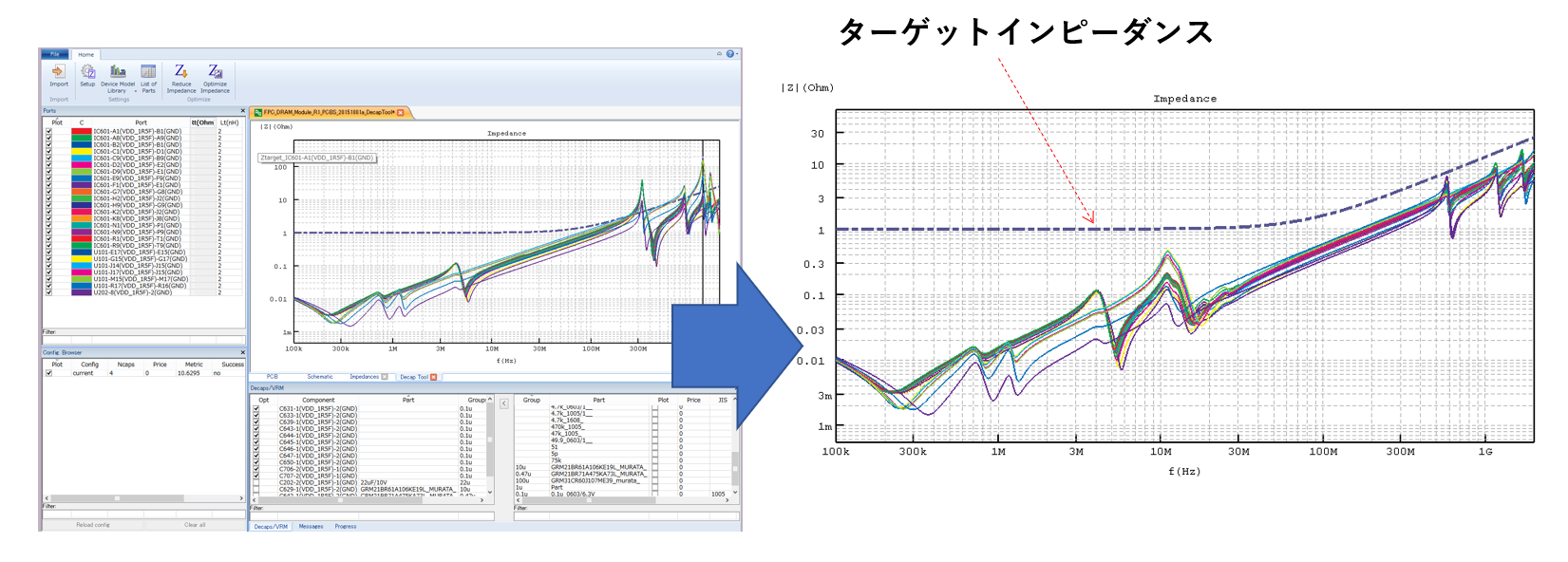

インピーダンス低減のため、デカップリングキャパシタ(パスコン)を追加実装します。 キャパシタの寄生インダクタンス成分(ESL)によって、反共振が生じるため、必要に応じて低ESLのキャパシタを採用する必要があります。 なお、目標の電源インピーダンスの達成に必要な最低限のデカップリングキャパシタの配置を検討する機能(パスコン最適化機能)も備わっています。 今回の設計では予め用意していた11ヶのうち、6ヶのキャパシタの配置で目標を満足することが判りました。

SI解析機能

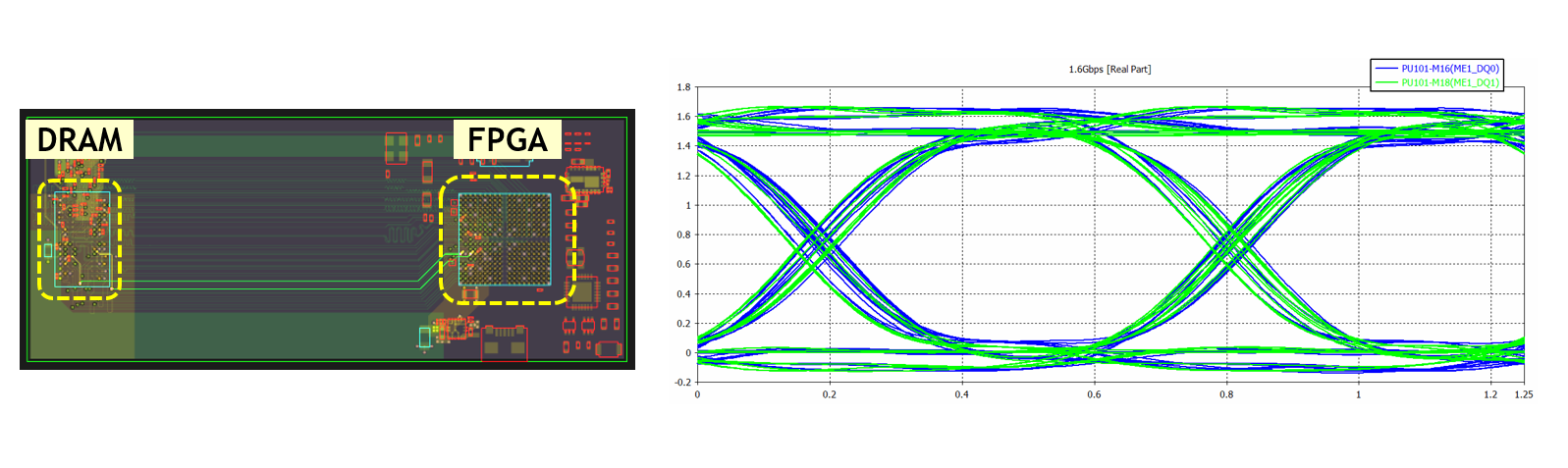

PCB Studioでは信号伝送特性の解析(時間軸、周波数軸)を高速に実行する機能も提供しています。 指定したNetに対して等価回路抽出を実行し、入出力部のデバイスを含めた回路シミュレーションを実行します。 一連のセットアップは自動的にバックグランドで実行されるため、設計基板に対して最小限の操作で伝送特性を評価することが可能となっています。 下図は、DRAMのLD0、DQ1における、Eye Diagramパターン(1.6Gbps)の解析結果です。 FPGA及びDRAMのI/OピンそれぞれにIBISモデルを割り当てることにより、ドライバ・レシーバ回路がNetに接続された状態で波形評価を行えます。

次に隣接する配線(DQ6と7)間のクロストークを周波数特性として確認した結果が以下のグラフです。 シンプルな操作で時間軸、周波数軸それぞれの高速信号伝送の評価を行うことができます。

CST Studio Suiteの導入を

ご検討のお客様

技術サポートをご提供致します。

まずはお気軽にご相談ください。

解析目的や現在直面している課題などお聞かせください。

- 会社名

- 株式会社エーイーティー

- 所在地

- 〒215-0033

神奈川県川崎市麻生区栗木2丁目7番6号

TEL:044-980-0505(代表)

お問い合わせ

お問い合わせ